- Pely insists that workloads require more independence than allows the execution of the main current of Lockstep allows

- Pely SC4S simulations demand mass efficiency improvements on previous generation designs

- Chip manufactured in TSMC 5 Nm with unusually large given size

In Hot Chips 2025, a small Japanese company known for unconventional hardware, presented its latest project, the Pely SC4s.

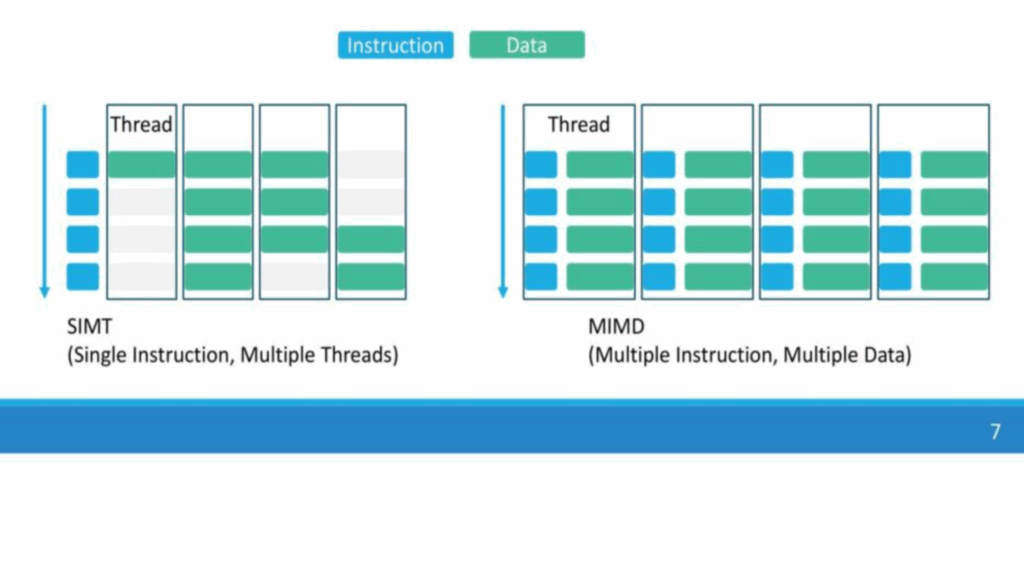

Unlike conventional chips manufacturers that have been standardized around the unique instruction, multiple data designs, Comporting Pely continues to look for multiple multiple data instructions (MIMD).

MIMD can be compared to a society of states, prefectures, cities and villages, where each unit acts with a certain degree of independence instead of following a single central authority.

Architecture and manufacturing options

MIMD is not a new idea: after all, each modern laptop for programming executes multiple tasks at the same time, but it has rarely been implemented on a truly massive scale that involves hundreds or thousands of nuclei.

Design philosophy assumes that future workloads will not always benefit from Lockstep execution and that the most independent thread management could be essential.

This makes its strategy different from the direction of most of the best CPU contenders that dominate the global market.

SC4S is manufactured in the 5 NM TSMC process and is not a small chip in terms of physical footprint.

With a given size of around 556 mm2, it is considerably larger than many consumer processors or work station.

However, the emphasis is not to minimize the silicon area, but in proveing whether the benefits of mass parallelism exceed costs.

The idea that CPUs have hundreds of nuclei has existed for a while. Pely argues that many small semi -autonomous nuclei can succeed where centralized approaches fight.

Indeed, the company is betting that computational demand in certain specialized domains justifies this scale, even if said approach may not be practical for a broader adoption of the consumer.

But what Pozy Computing launched are performance simulations instead of the final reference points of silicon, which naturally raises questions about how well these statements will be maintained in practice.

Compared to its previous SC3 design, it is projected that the SC4S deliver more than double energy efficiency by handling a DGEMM workload.

Meanwhile, the simulations of the Smith-Waterman algorithm, used in the alignment of the genome sequence, suggest almost an increase of four times in performance.

While these figures are impressive on paper, skepticism remains until independent tests validate them.

Historically, bold projections in the development of semiconductors have not always aligned with the results measured once real hardware is sent.

Although the SC4 are still under development, the company has already brought its attention to a successor.

The work is ongoing in a fifth generation processor, tentatively called Pely 5, which is expected to use a process of 3 nm or minor.

A launch window for 2027 has been established, although such long -term schedules in the development of chips often change due to technical or economic challenges.

Given the company’s scale, industry observers remain cautious about whether the timeline is realistic.

Via serve the house