- D-Matrix changes the focus of the training of inference hardware innovation

- The Corsair USA LPDDR5 and SRAM to cut HBM Reliance

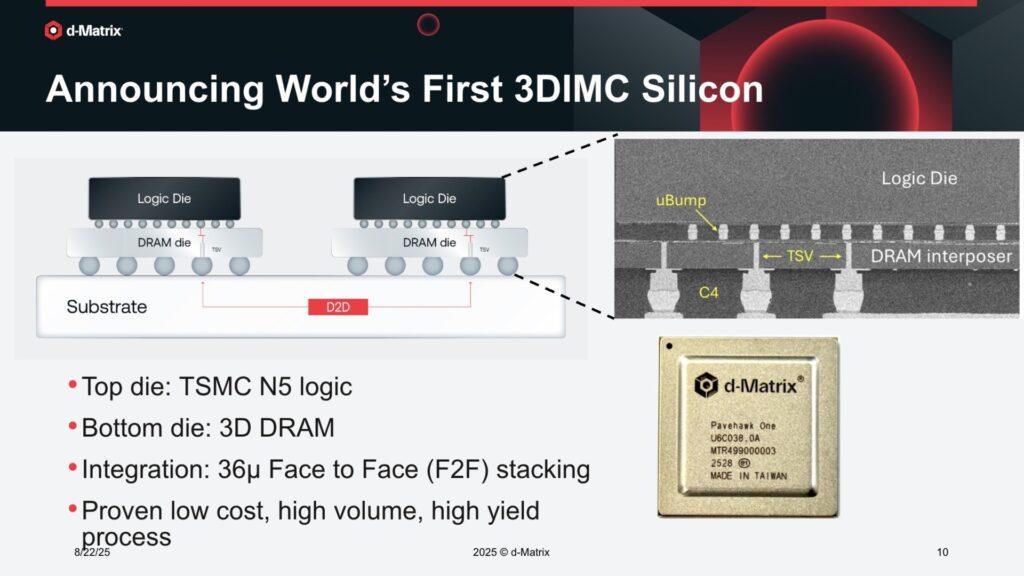

- Pavehawk combines dram and logic stacked for a lower latency

Sandisk and SK Hynix recently signed an agreement to develop “high bandwidth flash”, an alternative based on Nand to HBM designed to carry a larger and more volatile capacity to AI accelerators.

D-Matrix is now being positioned as a challenger of high bandwidth memory in the race to accelerate artificial intelligence workloads.

Although much of the industry has concentrated on training models that use HBM, this company has chosen to focus on the inference of AI.

A different approach to the memory wall

Its current design, the D-Matrix Corsair, uses a Chiplet-based architecture with 256 GB of LPDDR5 and 2 GB of SRAM.

Instead of pursuing more expensive memory technologies, the idea is to copalact acceleration and dram engines, creating a narrower link between computation and memory.

This technology, called D-Matrix Pavehawk, will be launched with 3DIMC, which is expected to rival HBM4 due to AI inference with 10x bandwidth and energy efficiency per battery.

Built in a TSMC N5 logic and combined with 3D -stacked play, the platform aims to bring computation and memory much closer than in conventional designs.

By eliminating some of the data transfer bottlenecks, D-Matrix suggests that it could reduce latency and energy use.

Looking at its technological route, D-Matrix seems compromised with layers of multiple dram trochers over logical silicon to push bandwidth and capacity.

The company argues that this stacked approach can offer an order of magnitude in performance profits while using less energy for data movement.

For an industry dealing with the limits of the memory interface scale, the proposal is ambitious, but is not composed.

It is worth noting that memory innovations around inference accelerators are not new.

Other companies have been experiencing well -coupled memory and computing solutions, including designs with controllers or links incorporated through interconnection standards such as CXL.

D-Matrix, however, is trying to go to integrating personalized silicon to rework the balance between cost, energy and performance.

The backdrop of these developments is the persistent challenge of costs and supply that surrounds HBM.

Large players like NVIDIA can ensure top -level HBM pieces, but smaller data centers or centers often have to settle for low speed modules.

This disparity creates an unequal playing field where access to faster memory directly shapes competitiveness.

If D-Matrix can comply with alternatives of lower cost and greater capacity, it would address one of the central pain points in scale inference at data center level.

Despite the “10x best performance” and “10x better energy efficiency” statements, D-Matrix is still at the beginning of what it describes as a several year trip.

Many companies have tried to address the so -called memory wall, however, few have restructured the market in practice.

The increase in AI tools and dependence on each LLM show the importance of scalable inference hardware.

However, it remains to be seen if Pavehawk and Corsair mature in widely adopted alternatives or will continue to be experimental.

Via serve the house