- SK Hynix split-cell 5-bit flash memory increases SSD density without significantly reducing production complexity

- RAID-0 style parallelism on split-cell NAND dramatically increases read speed

- Each half cell reduces voltage stress, extending the five-bit flash endurance.

The NAND flash industry continues to look for ways to increase storage density as demand from data centers, consumer devices, and artificial intelligence tools increases.

Conventional scaling through additional 3D NAND layers has become increasingly complex, expensive, and difficult to manufacture consistently.

While four-bit QLC flash memory is already in commercial production, moving to five-bit PLC flash memory remains impractical due to reliability and endurance issues related to voltage sense limits.

How split-cell flash changes the equation

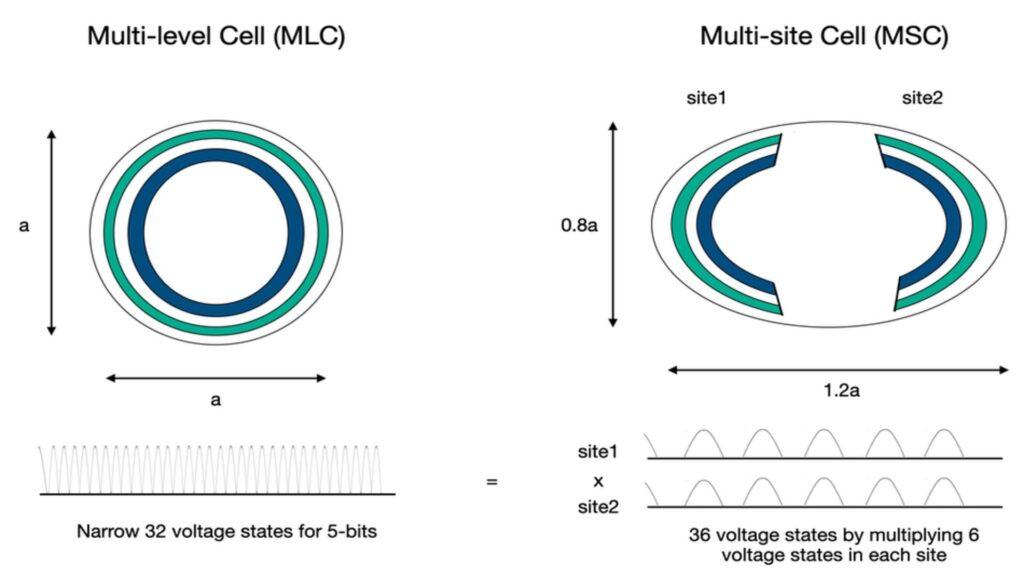

SK Hynix has introduced a different approach known as multisite cell technology. Instead of forcing a single NAND cell to maintain all 32 voltage states, the design splits the cell into two independent half-cells.

Each half stores six voltage states, which combine to represent a five-bit value. This design reduces voltage overhead while maintaining overall bit density.

The two half-cells operate in parallel as a single logical unit, resembling how RAID-0 distributes data between hard drives to increase performance.

In this case, the voltage states are combined during access rather than split between separate devices.

The physical shape of the cell is elliptical rather than circular, leaving room for an insulating wall between the halves and separate bitline connections.

SK Hynix claims that wider voltage gaps within each half-cell reduce electron leakage and shorten programming time.

The two halves are read simultaneously, which the company says offers faster read speeds compared to conventional PLC designs.

This method also improves resistance as lower voltage stress reduces cell wear.

SK Hynix demonstrated functional wafers at the IEDM 2025 conference, indicating the concept goes beyond simulation.

The split-cell approach requires additional semiconductor process steps, including cell division and gap filling, which adds cost and complexity.

As SK Hynix evaluates manufacturing capacity, other flash manufacturers including Samsung, Micron, Kioxia and Sandisk are expected to study similar ideas.

The concept doesn’t promise cheaper SSDs, just denser ones, and it doesn’t eliminate the role of hard drives in high-capacity storage.

If manufacturers can produce multisite cells at scale, PLC flash could finally become viable without the serious drawbacks seen in previous designs.

Through Blocks and files

Follow TechRadar on Google News and add us as a preferred source to receive news, reviews and opinions from our experts in your feeds. Be sure to click the Follow button!

And of course you can also follow TechRadar on TikTok for news, reviews, unboxings in video form and receive regular updates from us on WhatsApp also.